|

个人信息Personal Information

研究员 博士生导师

性别:男

学历:博士研究生毕业

学位:工学博士学位

-

为了满足现代无线通信系统的多频段多制式、小型化、低功耗、低成本、高数据率等要求,近年来面向5G移动通信等产业应用,进行了一系列超宽频射频/微波/毫米波集成电路研究。主研参与了科研项目十余项,含国家自然科学基金重点项目、面上项目,国家重点研发计划重点专项等。研制出多款高性能毫米波/太赫兹超宽带振荡器、频率源,探测器、数字功率放大器等芯片。部分代表成果如下:

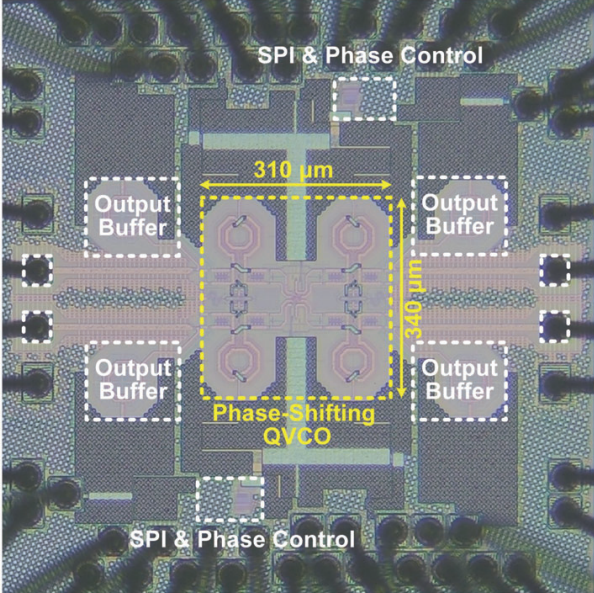

■ 提出360°任意相位调控振荡器新架构,针对高频相位控制面临的幅度-相位误差、相位精度有限、电路/功耗开销大等问题,提出相位调控频率源设计新范式,实现360°范围内任意相位高精度调控,天然具有恒定幅度优势。相关成果发表国际集成电路领域高水平会议IEEE CICC。

■ 提出G类阻抗调制多核功率振荡器新架构,提供了“多核合成扩容量、阻抗调制保效率、Class-G 供电增峰值”的系统级设计新范式,解决传统射频链路与时钟链路中功率-效率-噪声之间的矛盾。相关成果发表国际集成电路领域旗舰期刊IEEE JSSC。

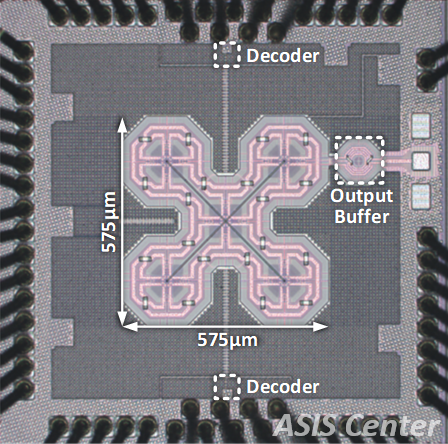

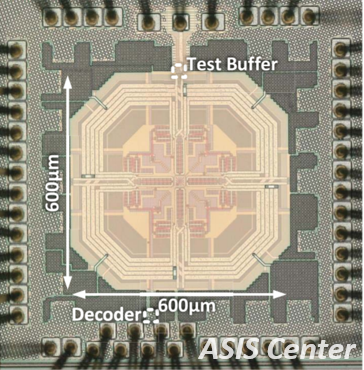

■ 提出核间整形多核振荡器新架构,突破传统共模整形技术的限制,同时提升共模与差模响应的品质因数,实现毫米波频段极低相位噪声信号直接生成,低误差敏感以及低寄生敏感的特性使该架构支持大规模多核扩展。相关成果发表国际集成电路领域旗舰会议IEEE ISSCC,入选ISSCC2023亮点论文。

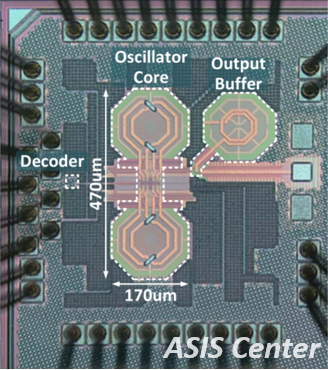

■ 提出离散耦合谐波阻抗扩展多核振荡器技术,解决了高性能振荡器难以同时实现低相噪以及高综合优值的难题,同时实现多核振荡器芯片小型化。相关成果发表国际集成电路领域旗舰会议IEEE ISSCC。入选ISSCC2021亮点论文,并受邀发表国际集成电路领域旗舰期刊IEEE JSSC。

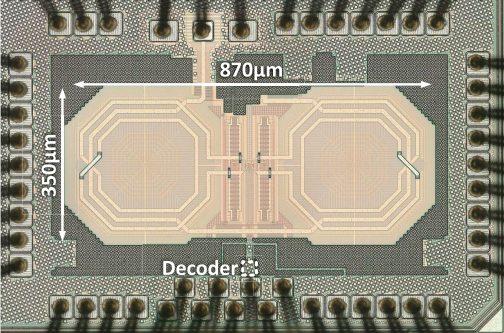

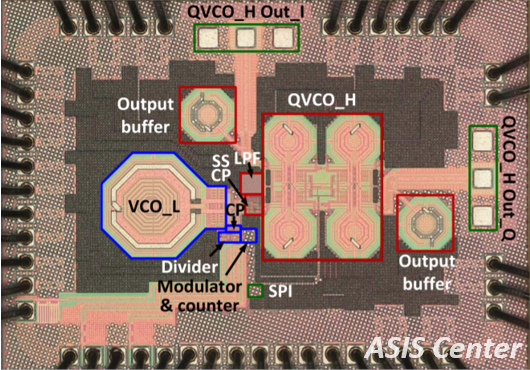

■ 提出混合电磁耦合模式倍增超宽频振荡器设计技术,频率范围达18.6-40.1GHz,首次实现单片振荡器同时覆盖各国5G毫米波标准,如24GHz,26GHz,28GHz,37GHz 与39GHz 等频段。实现10-MHz相噪频宽综合优值FoMT 203.6dBc/Hz,刷新业界毫米波FoMT极限。相关成果发表国际集成电路领域旗舰会议IEEE ISSCC、国际集成电路领域旗舰期刊IEEE JSSC。

■ 提出基于正交双模波形整型振荡器的级联式亚采样模式切换锁相环架构,实现毫米波宽频低相噪频率锁定以及宽频低正交相位误差。相关成果发表国际电路与系统领域旗舰期刊IEEE TCAS-I、射频集成电路领域高水平会议IEEE RFIC。

■ 提出小型化太赫兹多模振荡器技术,实现太赫兹宽频低相噪信号生成,芯片核心尺寸仅为国际同类工作六分之一,为片上宽频太赫兹信号源的阵列化集成提供了切实可行的方案。相关成果发表国际微波领域旗舰期刊IEEE TMTT、国际微波领域旗舰会议IEEE IMS。

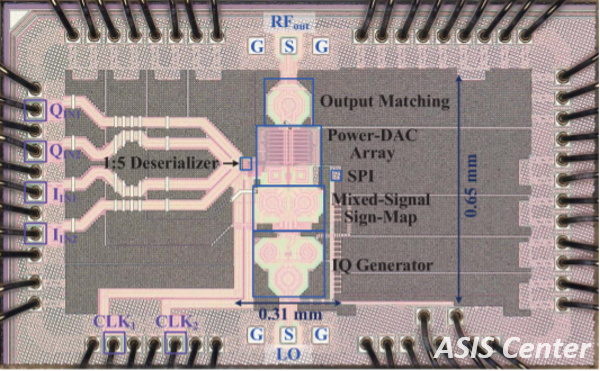

■ 参与研发基于陷波匹配的宽频数字毫米波正交发射机架构,研制20-32GHz数字正交发射机芯片,支持5G毫米波通信标准、3Gb/s高数据率传输,该工作为数字化功率放大器在毫米波频段的应用提供了理论与实验基础。相关工作发表国际集成电路领域旗舰期刊IEEE JSSC,射频集成电路领域高水平会议IEEE RFIC。

- Class-G Impedance-Modulation Multi-Core Power Oscillator for High Pout and Power Back-Off Efficiency Enhancement.IEEE JSSC 2025年

- A 28-GHz 189.2-dBc/Hz FoM 360° Phase-Shifting Quadrature Oscillator Without Phase Ambiguity Achieving 0.13° RMS Phase Error Under 2° Phase Resolution.IEEE CICC 2025年

- 7.8-to-10.7GHz Reliable-Mode-Switching Series Resonance Oscillator with Bidirectional Inductive-Mode-Pulling Achieving —156.5dBc/Hz Phase Noise and 199.2dBc/Hz FoMT at 10 MHz Offset in 40-nm CMOS.IEEE RFIC 2025年

- A 323.2 GHz Detector Using Harmonic Injection Locking with Polarization Diversity in 40nm CMOS.IEEE APMC 2025年

- A 21.8–41.6-GHz Fractional-N Subsampling PLL With Dividerless Unequal-REF-Delay Frequency Tracking.IEEE OJSSC 2025年

- A 7.8-11.9 Ghz Quad-Mode Class-F2,3 VCO with Multi-Stage Cross-Shared Common-Mode Path Achieving -131.9 dBc/Hz 1-MHz Phase Noise and 201.8 dBc/Hz FoMT.IEEE IMS 2025年

- 暂无内容

- 暂无内容

- 暂无内容